NI-Tutorial-6097-en.pdf

NI-Tutorial-6097-en.pdf

개요

멀티 코어 프로그래밍 기본 백서 시리즈

병렬 하드웨어는 컴퓨터 처리 기술에서 아주 흔한 요소가 되고있습니다. 한 때 단일 프로세서가 지배한 이후로, 칩 아키텍처는 이후 엔지니어들에게 큰 성능 향상을 할 수 있도록 진화했습니다. 다중 프로세서, 하이퍼 스레딩, 듀얼 코어, 멀티 코어와 FPGA를 포함하여 오늘날 시장에 있는 일반적인 병렬 하드웨어 아키텍처의 차이를 알아봅시다.

차례

1. 멀티 프로세서

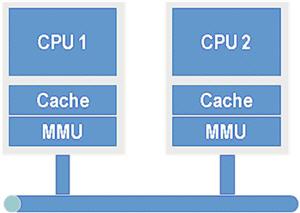

멀티 프로세서 시스템은 같은 칩에 있지 않은 다수의 CPU들을 포함합니다. 멀티 프로세서 시스템은 IT 서버의 목적으로 1990 년대에 일반적으로 되었습니다. 그 때 그것들은 보통 랙마운트 서버로 들어가는 프로세서 보드들의 형태였었습니다. 오늘날, 멀티 프로세서는 일반적으로 동일한 물리적 보드에 구성되고 고속 통신 인터페이스를 통해 연결됩니다.

그림 1. 멀티 프로세서 시스템은 long-interconnects을 가진 분리된 캐시 및 MMU를 가지고 있습니다.

멀티 프로세서 시스템은 멀티 코어 시스템보다 덜 복잡합니다, 왜냐하면 그들은 기본적인 단일 칩의 CPU들이 함께 연결된 것이기 때문입니다. 멀티 프로세서를 가진 시스템의 단점은 그들이 단일 칩 솔루션보다 비싼 여러 칩을 필요로하기 때문에들이 비싸다는 것입니다.

2. 하이퍼 스레딩

하이퍼 스레딩은 멀티 스레드 코드에 대한 지원을 개선의 주요 목적으로 하여 인텔에 의해 도입 된 기술입니다. 특정 작업 부하 환경에서 하이퍼 스레딩 기술은 기술에서 단일 프로세서상에서 병렬로 스레드를 실행함으로서 CPU 리소스의보다 효율적인 사용을 제공합니다.

하이퍼 스레딩 기술이 탑재된 프로세서가 운영체제에게 2개의 "논리적" 프로세서인 척하여, 운영체제가 동시에 두 개의 스레드 또는 프로세스를 예약 할 수 있도록 합니다. 하이퍼 스레딩의 장점은 다중 스레드 코드에 대한 개선된 지원, 즉 여러 스레드가 동시에 실행 할 수 있도록 하여, 향상된 반응 및 응답 시간을 제공합니다.

펜티엄 4 프로세서는 하이퍼 스레딩을 구현하는 CPU의 예입니다.

3. 듀얼 코어 및 멀티 코어 프로세서

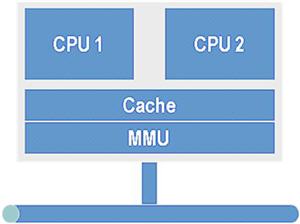

듀얼 코어 프로세서는 하나의 칩에 두 개의 CPU를 가지고 있습니다. 멀티 코어 프로세서는 2, 4, 8처럼 하나의 칩에 여러 개의 CPU 수를 포함하는 프로세서 패밀리입니다. 멀티 코어 프로세서에 대한 도전은 소프트웨어 발전 영역에 있습니다. 퍼포먼스 속도향상은 직접적으로 얼마나 애플리케이션의 소스 코드가 멀티 스레딩을 통해 병렬로 만들어졌는지에 관련이 있습니다.

그림 2. 멀티 코어 프로세서는 캐시 및 MMU를 short interconnects(짧은 상호연결)를 통해 공유합니다.

4. FPGAs

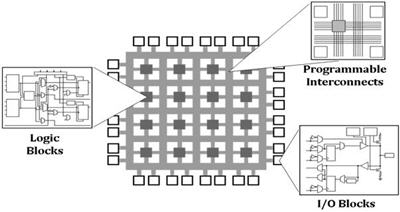

FPGA (필드 프로그래머블 게이트 어레이)는 재구성 가능한 게이트 어레이 논리 회로의 매트릭스를 포함하는 장치입니다. FPGA가 구성되면, 내부 회로는 소프트웨어 애플리케이션의 하드웨어 구현을 생성하는 방식으로 접속됩니다. 프로세서와 달리, FPGA는 처리 로직을위한 전용 하드웨어를 사용하며, 운영 체제를 갖고 있지 않습니다.

단일 FPGA는 단일 집적 회로 (IC) 칩에 논리 게이트의 수백만을 통합하여 개별 부품 수천을 대체 할 수있습니다. FPGA 칩의 내부는 그 I / O 블록의 주변에 의해 둘러싸인 구성 가능한 로직 블록 (CLB) 매트릭스로 구성되며, 신호들은 프로그래머블 인터 커넥터 스위치 및 와이어 라우트에 의해 FPGA 매트릭스 내에서 라우팅됩니다.

그림 3. FPGA는 사용자가 병렬 하드웨어 경로로 게이트를 프로그램하는 것을 허용합니다.

FPGA는 단순히 거대한 부분의 프로그래머블 게이트이기 때문에, 그들은 많은 병렬 하드웨어 경로로 프로그래밍 될 수 있습니다. FPGA는 정말로 자연적으로 병렬적이어서 다른 처리 작업이 같은 리소스에 대해 경쟁할 필요가 없습니다. 프로그래머들은 자동으로 FPGA 패브릭에 직접 그들의 솔루션을 매핑 할 수 있습니다. 이것은 사용자가 FPGA 칩 내부에서 동시 병렬 회로와 같이 모두 수행되는 어떤 수의 작업-지정된 코어들을 생성할 수 있도록 합니다.

하드웨어 실행은 대부분의 프로세서 기반 소프트웨어 솔루션보다 큰 성능과 결정성을 제공합니다. FPGA의 논리 게이트의 병렬 특성은 데이터의 매우 높은 처리량을 할 수 있습니다. 일단 코드가 컴파일되하 FPGA 상에서 실행 된 후에는 대부분의 OS에서 일반적인 소프트웨어 실행 및 스레드 우선 순위와 관련하여 지터없이 실행될 것입니다. 그리고 실시간 운영체제에서는 보다 더 적은 정도로 제공할 것입니다.

자세한 내용은 다음 웹 사이트를 방문 : 병렬 실행 및 파이프 라인 : 당신의 LabVIEW FPGA VI를 최적화

5. 방법의 LabVIEW 프로그램 병렬 하드웨어

LabVIEW는 1998 년에 도입 된 버전 5.0부터 멀티 스레드되었습니다. 의 LabVIEW의 데이터 흐름 자연 병렬 코드가 쉽게 병렬 하드웨어에 매핑 할 수 있습니다. 따라서, 멀티 프로세서, hypertheaded 및 다중 코어 프로세서 시스템을 타겟팅 이상적인 개발 언어이다.

FPGA 프로그래밍의 경우, LabVIEW는 자동으로 자일링스의 FPGA를 타겟으로 할 수있는 비트 스트림으로 컴파일 VHDL 코드를 생성합니다.

6. 멀티 코어 프로그래밍에 대한 자세한 자료

멀티 코어 프로그래밍 기본 백서 시리즈

'OS' 카테고리의 다른 글

| [OS] rm에 대한 이해 (0) | 2014.05.28 |

|---|---|

| [OS] 디렉토리 권한이 777이면 다른 사용자의 파일을 삭제할 수 있다? (0) | 2014.05.28 |

| [OS] Permissions (0) | 2014.05.28 |

| [OS] syslog (0) | 2014.04.17 |

| /etc/shadow 파일에서 !와 !!, * 차이 (0) | 2014.04.02 |

| [OS] What is NUMA? (0) | 2014.03.14 |

| Selecting the MMU Virtualization Mode (0) | 2014.03.07 |

| 메모리 관리 장치에 대하여 (0) | 2014.03.07 |

| [OS] script 명령어를 이용한 터미널 세션 공유 (0) | 2014.01.29 |

| [OS] du -s 와 df 의 결과가 다른 이유 (0) | 2009.02.13 |